梳理fpga中的setup time和hold time。

简单理解

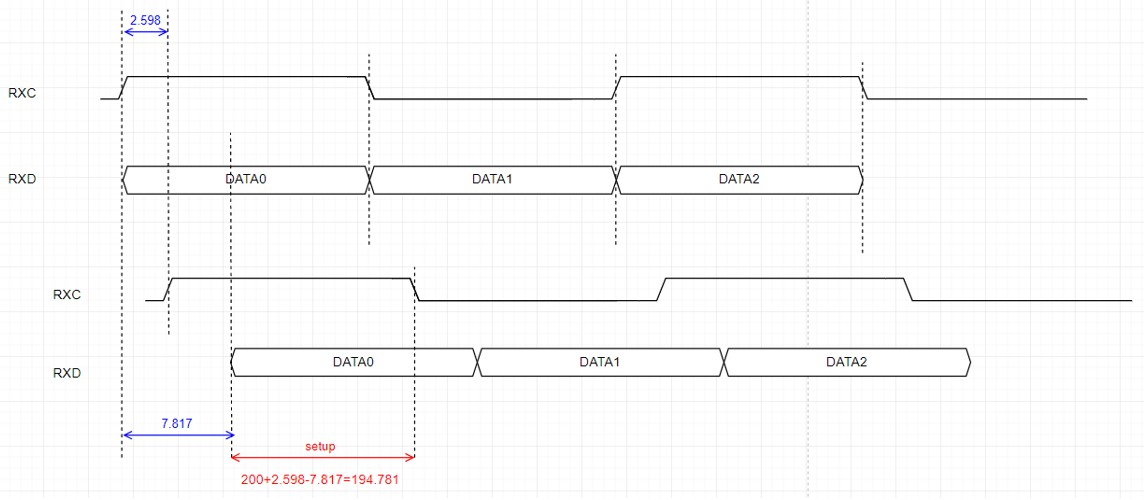

一般前仿中波形是这样的:

若是加上延迟,会变成这样的:

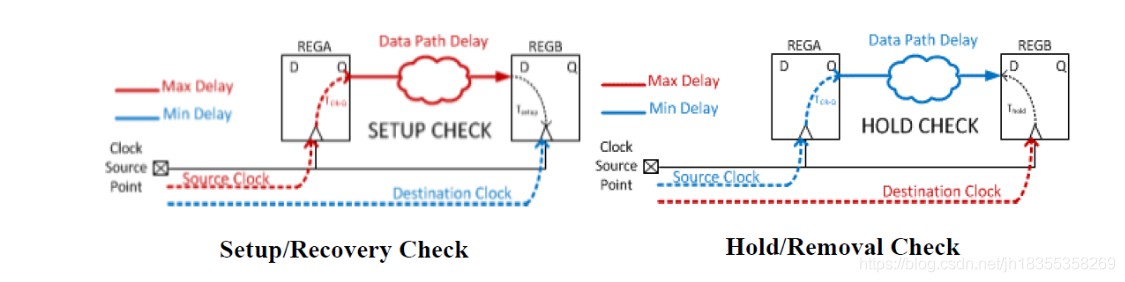

setup check就是让data path delay最大,clock path delay最小。

hold check就是让data path delay最小,clock path delay最大。

专业理解一(转载)

1、基本概念

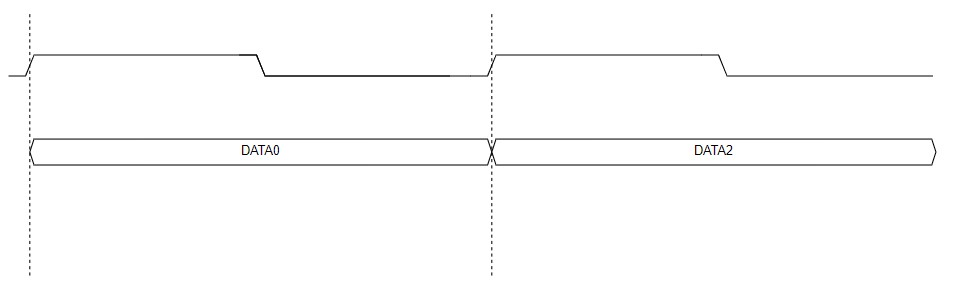

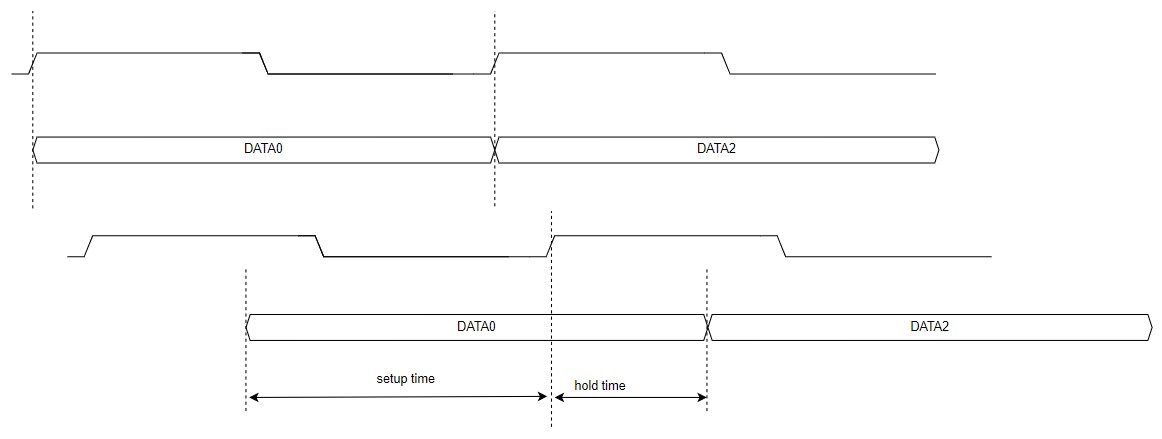

setup time是指在时钟有效沿(下图为上升沿)之前,数据输入端信号必须保持稳定的最短时间。

hold time是指在时钟有效沿(下图为上升沿)之后,数据输入端信号必须保持稳定的最短时间。hold time时序检查确保新数据不会在触发器稳定输出初始数据之前过早到达D端而覆盖其初始数据。

2、Setup & Hold详细分析

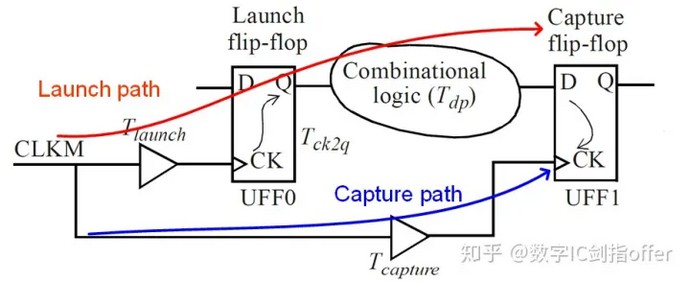

发送数据的触发器称为Launch flip-flop,接收/捕获数据的触发器称为Capture flip-flop。两触发器时钟端信号为同一时钟。

如图所示,launch_path为:

CLKM→BUF(launch)→UFF0/CK→UFF0/Q→Comb_logic→UFF1/D;

capture path为:

CLKM→BUF(capture)→UFF1/CK;

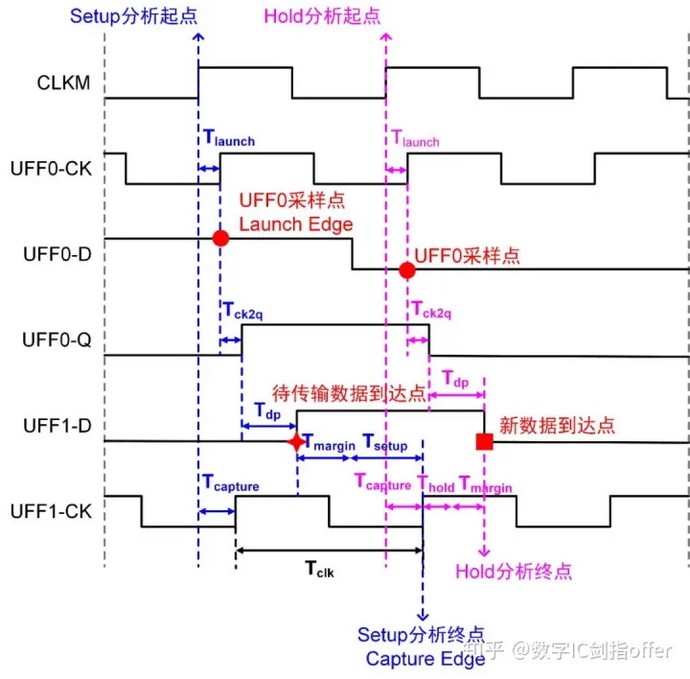

(1)Setup Time

两触发器间的数据传输通常在一个时钟周期内完成。

数据到达UFF1/D所需时间Arrival time为:

Ta = T_launch + T_ck2q + T_dp

满足setup要求时所允许的最长时间Required time为:

Tr = T_capture + T_clk - T_setup

因此setup time要求可表示为:Tr - Ta = T_margin >= 0。

根据图4,setup time要求还可表示为:

T_launch + T_ck2q + T_dp + T_margin + T_setup = T_capture + T_clk

其中:

T_launch:CLKM到UFF0时钟端CK的延时

T_ck2q:UFF0的CK->Q的传输时间

T_dp:组合逻辑延时

T_margin:设计裕量

T_setup:UFF1的setup时间要求

T_capture:CLKM到UFF1时钟端CK的延时

T_clk: 时钟周期

由此可见,setup检查发生在不同时钟边沿,与时钟频率有关。

(2)Hold Time

数据到达UFF1/D所需时间Arrival time为:

Ta = T_launch + T_ck2q + T_dp

满足hold要求时所允许的最短时间Required time为:

Tr = T_capture + T_hold

因此hold time要求可表示为:Ta - Tr = T_margin >= 0。

根据图4,hold time要求还可表示为:

T_launch + T_ck2q + T_dp = T_capture + T_hold + T_margin

其中:

T_launch:CLKM到UFF0时钟端CK的延时

T_ck2q:UFF0的CK->Q的传输时间

T_dp:组合逻辑延时

T_hold:UFF1的hold时间要求

T_margin:设计裕量

T_capture:CLKM到UFF1时钟端的延时

T_clk: 时钟周期

由此可见,hold检查发生在同一时钟边沿,与时钟频率无关。

(3)总结

setup time是针对Capture edge来说,待传输数据不能来太晚;hold time是针对Capture edge来说,新数据不能来太早,以确保待传输数据保持一段时间。总结为一句话:当前待传输的数据,相对于Capture edge来说,必须早来(setup time)晚走(hold time)。

3、Setup & Hold违例解决方法

(1)Setup需满足以下条件:

T_launch + T_ck2q + T_dp + T_setup <= T_capture + T_clk

记Clock Skew: T_skew = T_capture- T_launch,即:

T_ck2q + T_dp + T_setup <= T_skew + T_clk

因此,setup violation修复方法包括:

① T_clk:增加T_clk,也就是降频

② T_dp:优化组合逻辑延时,具体包括:

a. 增加一个中间触发器来切割Timing Path,分割组合逻辑延时(流水线结构)

b. 对于有较大负载的节点可以考虑插buffer、逻辑复制的方法来优化扇出,减少关键路径上的负载(插Buffer,逻辑复制)

c. 小Cell换成大Cell,更换更大驱动的Cell,增强驱动能力

d. 更换SVT/LVT的Cell

③ T_skew:采用positive skew(T_skew >0),但是要注意可能引入的hold问题,以及前后级的margin问题

④ T_ck2q:更换更快的时序逻辑单元,如HVT->LVT

(2)Hold需满足以下条件:

T_launch + T_ck2q + T_dp >= T_capture + T_hold

记Clock Skew: T_skew = T_capture- T_launch,即:

T_ck2q + T_dp >= T_skew + T_hold

因此,hold violation修复方法包括:

① T_dp:增加组合路径延时,通过插buffer、插delay cell、更换驱动、更换阈值的方法(组合逻辑深度的增加会增加芯片的面积、布线资源、功耗,可能产生在慢速工艺库条件下建立时间违例)

② T_skew:减小skew,甚至采用negative skew,但需做好时钟树的balance。

③ 插入低电平有效的锁存器(Lock-up Latch):高电平期间,锁存器输出保持不变,相当于人为将数据推迟了半个时钟周期,以保证满足hold时间要求。

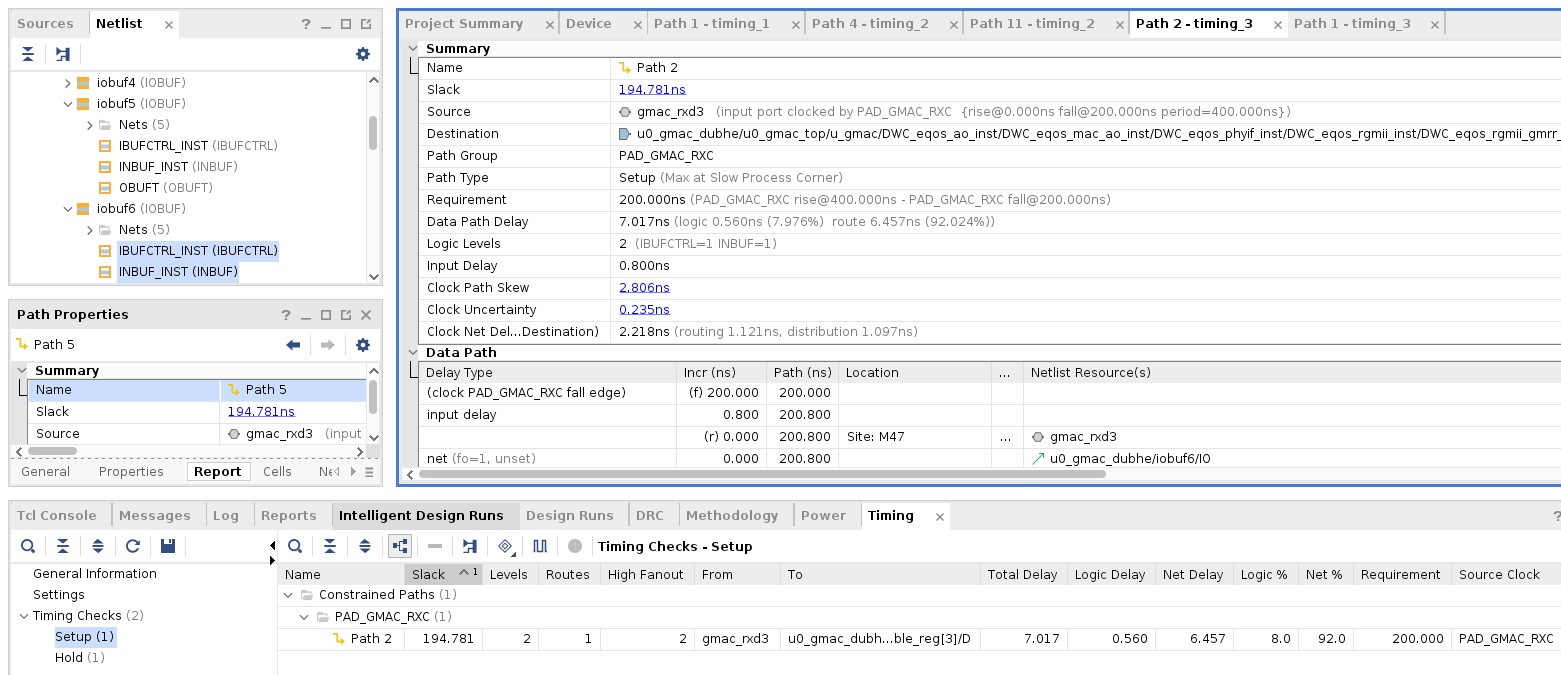

FPGA时序报告

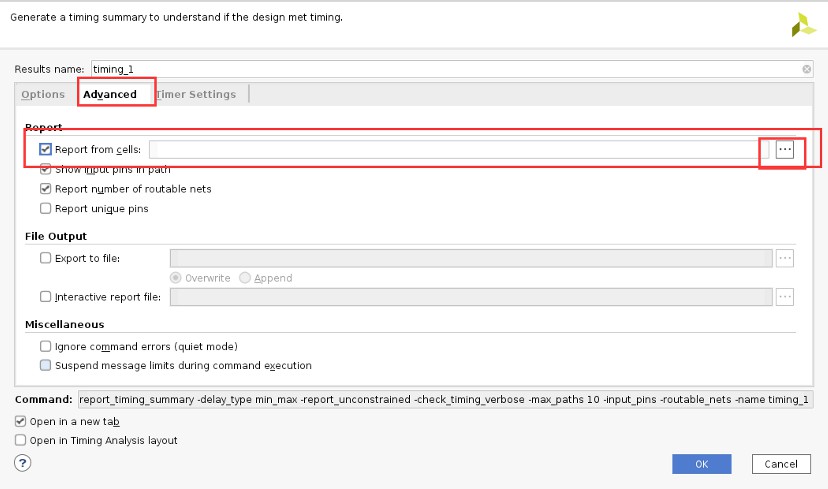

如下操作可以产生某条路径的时序报告。

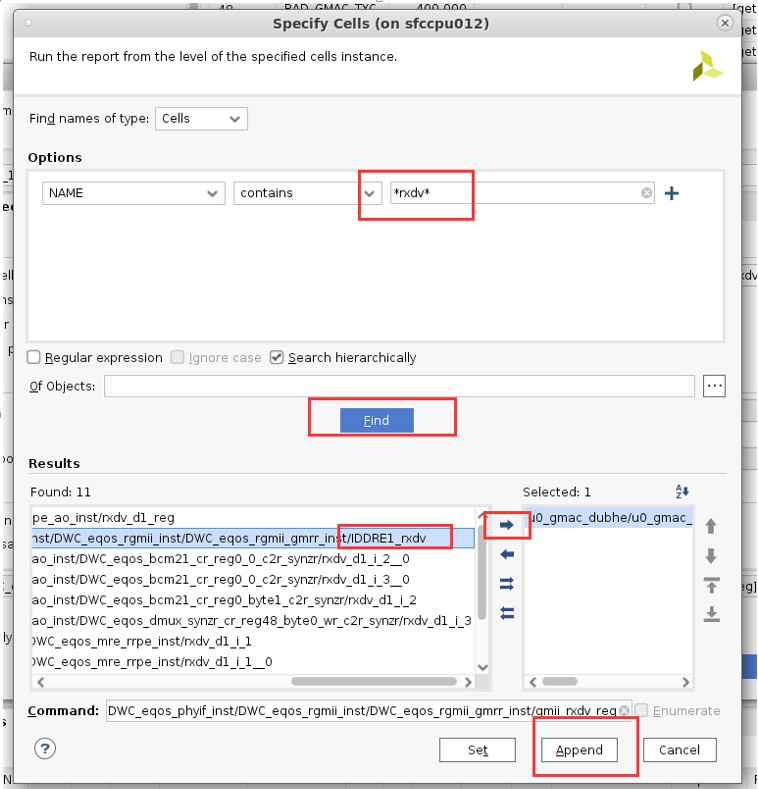

Open Implemented Design -> Report Timing Summary -> Advanced -> Report From cells

输入信号名 -> Find -> 选中信号 -> Append

就能看到类似的报告了,有setup,也有hold。

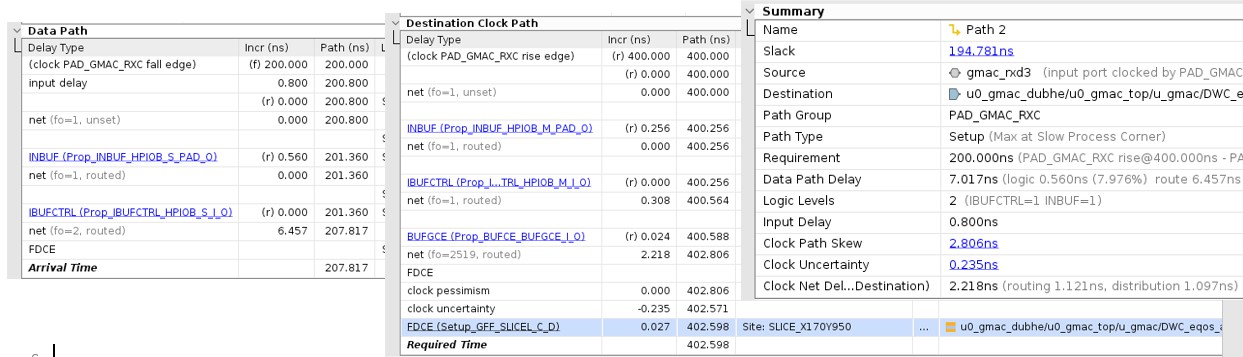

从setup报告中可以看到:

- input delay = 0.80

- data path delay = 7.017

- clock path delay = 2.598

从而,可以画出图。并且计算出slack,和报告中的slack是对应起来的。